### 低価格・中速 SIP 固定ディレイライン

#### 特 長

FDGタイプは、エルメックが得意とする高速ディレイラインの構造を基に、 内部素子の区間数だけを 1/2 ~ 1/3 程度に減らした、中速域の SIP 固定ディ レイラインです。

区間数を減らした事により、通過帯域はFDC/FDDタイプの約半分と狭く なりますが、その分安価にてご提供可能です。クロック 1/2 周期以内の調整 であればFDGタイプで充分対応可能です。

本製品は、RoHS対応品で、端子はNi下地Snメッキとなっております。

### 共通仕様

インピーダンス FDG1E205のみ50 $\Omega$ ±10%

上記以外の品番は100Ω±10%

200Ωで25nsまで、500Ωであれば10nsまで設計 可能ですので、回路の低消費電力化等の目的 でより高いインピーダンスのディレイラインをお 探しの場合はお気軽にご相談下さい。

波形歪 オーバーシュート/プリシュート±20%未満

-50**~**+200ppm/°C 遅延時間温度係数 絶縁抵抗 DC50V、100MΩ以上 DC50V、1分間 耐圧

使用温度範囲  $-40^{\circ}\text{C} \sim +85^{\circ}\text{C}$  $-40^{\circ}$ C $\sim+120^{\circ}$ C 保存温度範囲

#### 仕 様

| 品 番      | 遅延時間        | 出力立上り時間              | -3dB通過帯域<br>(保証値) | 直流抵抗值      |

|----------|-------------|----------------------|-------------------|------------|

| FDG1010  | 1ns±0.2ns   | (20%~80%)<br>0.6ns以下 | DC~600MHz         |            |

| FDG1010  | 2ns±0.2ns   | 0.6ns以下              | DC~600MHz         |            |

| FDG3010  | 3ns±0.3ns   | 0.9ns以下              | DC~400MHz         | 1.0Ω以下     |

| FDG4010  | 4ns±0.3ns   | 1.2ns以下              | DC~300MHz         |            |

| FDG5010  | 5ns±0.4ns   | 1.4ns以下              | DC~250MHz         |            |

| FDG6010  | 6ns±0.5ns   | 1.8ns以下              | DC~200MHz         | 1.5Ω以下     |

| FDG7010  | 7ns±0.5ns   | 2.0ns以下              | DC~180MHz         | 1.01.00.1  |

| FDG8010  | 8ns±0.6ns   | 2.4ns以下              | DC~150MHz         |            |

| FDG9010  | 9ns±0.7ns   | 2.5ns以下              | DC~140MHz         | 2.0Ω以下     |

| FDG10010 | 10ns±0.7ns  | 3.0ns以下              | DC~120MHz         | 2.011 00 1 |

| FDG11010 | 11ns±0.8ns  | 3.2ns以下              | DC~110MHz         |            |

| FDG12010 | 12ns±0.9ns  | 3.5ns以下              | DC~100MHz         | 0 —        |

| FDG13010 | 13ns±1.0ns  | 3.7ns以下              | DC~95MHz          | 2.5Ω以下     |

| FDG15010 | 15ns±1.1ns  | 4.2ns以下              | DC~85MHz          |            |

| FDG16010 | 16ns±1.2ns  | 4.4ns以下              | DC~80MHz          | 3.0Ω以下     |

| FDG18010 | 18ns±1.3ns  | 5.0ns以下              | DC~70MHz          | 4.0Ω以下     |

| FDG20010 | 20ns±1.4ns  | 5.5ns以下              | DC~65MHz          |            |

| FDG22010 | 22ns±1.6ns  | 5.5ns以下              | DC~65MHz          | 4.5Ω以下     |

| FDG25010 | 25ns±1.8ns  | 7.0ns以下              | DC~50MHz          | 10.0Ω以下    |

| FDG30010 | 30ns±2.1ns  | 9.0ns以下              | DC~40MHz          | 15.0Ω以下    |

| FDG35010 | 35ns±2.5ns  | 10.0ns以下             | DC~35MHz          | 17.0Ω以下    |

| FDG40010 | 40ns±2.8ns  | 12.0ns以下             | DC~30MHz          | 18.0Ω以下    |

| FDG45010 | 45ns±3.2ns  | 14.0ns以下             | DC~25MHz          | 19.0Ω以下    |

| FDG50010 | 50ns±3.5ns  | 18.0ns以下             | DC~20MHz          | 21.0Ω以下    |

| FDG1E205 | 100ns±7.0ns | 35.0ns以下             | DC~10MHz          | 21.032以下   |

## 低価格・中速 SIP 固定ディレイライン

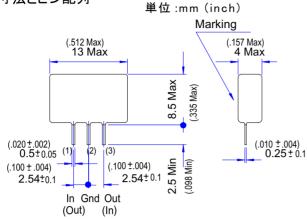

### 外形寸法とピン配列

### はんだ付け条件

フローはんだ:260℃、10秒以内 はんだ鏝:350℃、5秒以内

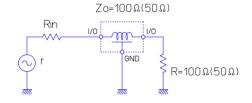

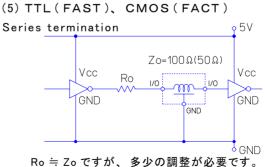

### 適用例とその終端方法

### (1) アナログ回路

r:信号源のインピーダンス

Rin: 入力整合抵抗

Zo:内部素子の特性インピーダンス

(= 出 カインピーダンス)

Ro:内部整合抵抗(=Zo)

r + Rin = Zo = R

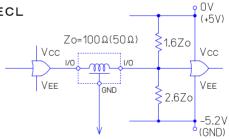

#### (2) ECL(-2V終端ライン使用)

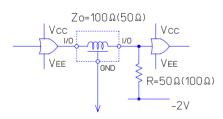

(3) PECL

V<sub>cc</sub>、V<sub>ee</sub>、-2Vのいずれかの電圧ラインへ接続

V<sub>cc</sub>、V<sub>ee</sub>のいずれかの電圧ラインへ接続

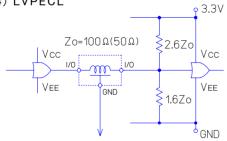

### (4) LVPECL

3.3V、GND のいずれかの電圧ラインへ接続

### FDG タイプ

# 低価格・中速 SIP 固定ディレイライン

### 特性例(1)

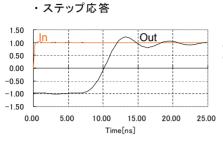

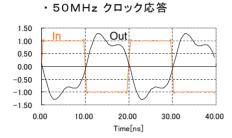

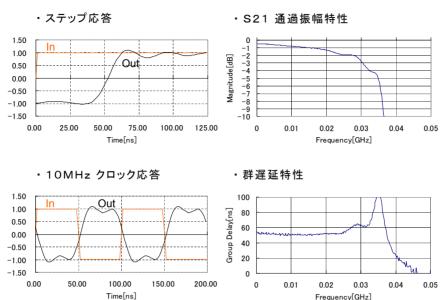

### (1) FDG10010

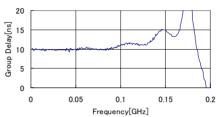

#### • 群遅延特性

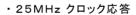

#### (2) FDG20010

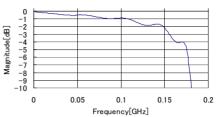

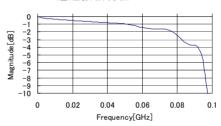

### ·S21 通過振幅特性

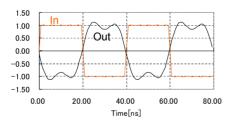

• 群遅延特性

### FDG タイプ

# 低価格・中速 SIP 固定ディレイライン

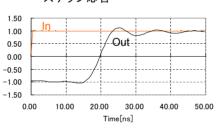

### 特性例(2)

### (3) FDG50010

### RoHS 対応状況

- (1) 対応状況 発売当初より、RoHS 対応品です。

- (2) 端子のメッキ仕様Ni 下地 、Sn メッキ